# **EPC®-6315 Hardware** Reference

April 2005

Copyright ©2005 by RadiSys Corporation.

All rights reserved.

EPC and RadiSys are registered trademarks of RadiSys Corporation. ASM, Brahma, DAI, DAQ, MultiPro, MultiPro, Promentum, SAIB, Spirit, and ValuePro are trademarks of RadiSys Corporation.

DAVID, MAUI, OS-9, OS-9000, and SoftStax are registered trademarks of RadiSys Microware Communications Software Division, Inc. FasTrak, Hawk, and UpLink are trademarks of RadiSys Microware Communications Inc.

All other trademarks, registered trademarks, service marks, and trade names are the property of their respective owners.

# Before you begin

This guide describes EPC-6315, a PrPMC (Processor PCI Mezzanine Card) that uses the RadiSys 82600 integrated chipset to bring an Intel<sup>†</sup> Architecture processor into ultra-dense form factors. This guide is for hardware and software designers, engineers, and those with a electronics and/or programming knowledge who need to understand the EPC-6315 operation.

# About this guide

### **Contents**

| Chapter/appendix |                                | Description                                                                                                                                                    |

|------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | Introduction                   | Introduces the EPC-6315, briefly describes its features, and lists specifications.                                                                             |

| 2                | Configuration and installation | Explains how to install and remove the EPC-6315 from a main board.                                                                                             |

| 3                | Operating System Installation  | Explains how to install Linux† and VxWorks† operating systems on your EPC-6315.                                                                                |

| 4                | BIOS configuration             | Explains how to configure the BIOS using the built-in BIOS setup menus.                                                                                        |

| 5                | Theory of operation            | Describes how EPC-6315 components provide a CompactPCI bus compatible embedded computer with standard PC peripherals plus PCI and ISA interfaces.              |

| A                | Message codes                  | Maps the addresses used for I/O and by the chipset registers.                                                                                                  |

| В                | Interrupts                     | Lists DMA channel and IRQ assignments to the peripherals supported by the EPC-6315.                                                                            |

| С                | Connectors                     | Details the location, form, and pinouts of the connectors used in the EPC-6315.                                                                                |

| D                | Error messages                 | Provides explanations of common error messages and start-up codes.                                                                                             |

| Ε                | Flash memory addresses         | Lists the EPC-6315 flash chip's major sections.                                                                                                                |

| F                | Re-programming the flash chip  | Details how to update or recover your system BIOS,<br>Flash Boot Device (FBD), and Boot Block by<br>re-programming all or part of the EPC-6315's<br>flash chip |

| Chapter/appendix |                     | Description                                                                                                                                            |

|------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| G                | Carrier card design | Provides guidelines for designing a carrier card that supports Monarch mode.                                                                           |

| Н                | EPC-6315 test board | Provides guidelines for designing a a full ATX sized, four PMC site circuit board to begin production, test, and early development using the EPC-6315. |

### **Notational conventions**

This manual uses the following conventions:

- Screen text and syntax strings appear in this font.

- All numbers are decimal unless otherwise stated.

- Bit 0 is the low-order bit. If a bit is set to 1, the associated description is true unless otherwise stated.

Notes indicate important information about the product.

Tips indicate alternate techniques or procedures that you can use to save time or better understand the product.

The globe indicates a World Wide Web address.

The book indicates a book or file.

ESD cautions indicate situations that may cause damage to hardware via electro-static discharge (ESD).

Cautions indicate potentially hazardous situations which, if not avoided, may result in minor or moderate injury, or damage to data or hardware. It may also alert you about unsafe practices.

Warnings indicate potentially hazardous situations which, if not avoided, can result in death or serious injury.

Danger indicates imminently hazardous situations which, if not avoided, will result in death or serious injury.

# Where to get more information

### About EPC-6315

You can find out more about EPC-6315 from these sources:

- Readme file: Lists features and issues that arose too late to include in other documentation.

- World Wide Web: RadiSys maintains an active site on the World Wide Web. The site contains current information about the company and locations of sales offices, new and existing products, contacts for sales, service, and technical support information. You can also send e-mail to RadiSys using the web site.

When sending e-mail for technical support, please include information about both the hardware and software, plus a detailed description of the problem, including how to reproduce it.

To access the RadiSys web site, enter this URL in your web browser:

http://www.radisys.com

Requests for sales, service, and technical support information receive prompt response.

• Other: If you purchased your RadiSys product from a third-party vendor, you can contact that vendor for service and support.

### About related RadiSys products

82600 High Integration Dual PCI System Controller Data Book: This book details the RadiSys 82600 High Performance System Controller, a member of the RadiSys family of long-life embedded PC compatible core logic. The 82600 is a highly integrated single chip implementation of all requirements of a high performance Compact PCI Central Resource and Peripheral Bridge including the North Bridge, South Bridge, PCI to PCI Bridge, and a selected set of Super I/O functions targeted at embedded, PC-compatible systems. It supports Intel Celeron<sup>†</sup>, Pentium II, and Pentium III processors with 66MHz, 100MHz and 133MHz system bus frequencies.

### About related EPC-6315 components

Processor PMC standard, VITA 32-199X, Draft 0.41 PCI Specification, Revision 2.2

### Other

- For MV Linux<sup>†</sup> LSPs, contact MontaVista at this URL: http://www.mvista.com

- For VxWorks<sup>†</sup> BSPs, contact RadiSys or WindRiver http://www.windriver.com http://www.radisys.com

# Contents

| Before you begin                                     |     |

|------------------------------------------------------|-----|

| About this guide                                     | iii |

| Contents                                             | iii |

| Notational conventions                               | iv  |

| Where to get more information                        | iv  |

| About EPC-6315                                       | iv  |

| About related RadiSys products                       | v   |

| About related EPC-6315 components                    | V   |

| Other                                                | v   |

| Chapter 1: Introduction                              |     |

| Features                                             | 2   |

| Compatibility                                        | 2   |

| Intel Tualatin LP processors in micro-FCBGA package  | 2   |

| Specifications                                       | 3   |

| Environmental                                        | 3   |

| Additional specifications                            | 5   |

| Chapter 2: Configuration and installation            |     |

| Before you begin                                     | 8   |

| Installing the EPC-6315 PMC on the carrier card      | 8   |

| Using the 3-pin connector                            | 9   |

| Maintaining and upgrading the EPC-6315               | 10  |

| Disconnecting the EPC-6315 PMC from the carrier card | 10  |

| Chapter 3: Operating System Installation             |     |

| Installing Red Hat Linux                             | 11  |

| Installing Red Hat on a separate computer            | 11  |

| Installing Red Hat 7.3 or later over the serial port | 12  |

| Installing MontaVista Linux                          | 14  |

| Configure the host to boot EPC-6315 over the network | 14  |

| Extract the kernel source and filesystem             | 14  |

| Configure DHCP                                       | 14  |

| Configure TFTP                                       | 15  |

| Red Hat 7.x                                          | 16  |

| Configure NFS                                        | 16  |

| Network boot the kernel                              | 16  |

| Install MontaVista Linux to a hard drive             | 17  |

| Installing VxWorks                                   | 19  |

| Requirements                                         | 19  |

| Installation                                         | 20  |

| Chapter 4: BIOS configuration                        |     |

| BIOS setup screens                                   | 2.3 |

| Menu map                                      | 24 |

|-----------------------------------------------|----|

| Navigation                                    | 24 |

| Main Setup menu                               | 25 |

| Primary Master/Slave sub-menus                | 27 |

| Advanced menu                                 | 31 |

| PCI Configuration sub-menu                    | 33 |

| PrPMC customizations sub-menu                 | 34 |

| PCI/PNP ISA UMB Region Exclusion sub-menu     | 36 |

| PCI/PNP ISA IRQ Resource Exclusion sub-menu   | 37 |

| Cache Memory sub-menu                         | 38 |

| Console Redirection sub-menu                  | 43 |

| I/O Device Configuration sub-menu             | 45 |

| Boot menu                                     | 46 |

| Exit menu                                     | 48 |

| CMOS Save & Restore sub-menu                  | 49 |

| Chapter 5: Theory of operation                |    |

| Organization                                  | 52 |

| Block diagram                                 | 52 |

| Intel Tualatin-LP 512K processor              | 52 |

| Speed and voltages                            | 53 |

| Clocking                                      | 53 |

| RadiSys 82600 system controller               | 54 |

| Power-up configuration.                       | 55 |

| Host bridge                                   | 56 |

| Memory subsystem                              | 56 |

| Memory map                                    | 56 |

| BIOS flash support                            | 57 |

| Dual PCI bus architecture                     | 58 |

| Local PCI bus                                 | 59 |

| PCI Ethernet controller                       | 59 |

| PCI interrupts                                | 59 |

| IDE controller flash disk                     | 60 |

| RTC                                           | 60 |

| Serial port                                   | 60 |

| Keyboard and mouse controller                 | 60 |

| Power                                         | 61 |

| Avoiding memory address and data misalignment | 62 |

| Appendix A: Message codes                     | 63 |

|                                               |    |

| Appendix B: Interrupts                        | 65 |

| Appendix C: Connectors                        |    |

| Connector locations                           | 67 |

| CompactPCI connector                          | 68 |

| J1 connector                                  | 68 |

| PMC connectors                                | 69 |

| Jn1 connector                                 | 69 |

| Jn2 connector                                 | 70 |

| Jn4 connector                                 | 71 |

| Ethernet port                                 | 75 |

| CompactFlash socket                           | 75  |

|-----------------------------------------------|-----|

| 3-pin connector                               | 76  |

| Null-modem serial cable                       | 76  |

| Appendix D: Error messages                    | 77  |

| Appendix E: Flash memory addresses            |     |

| Appendix F: Re-programming the flash chip     |     |

| About the flash chip                          | 81  |

| About re-programming the flash chip           |     |

| Before you begin                              |     |

| Creating a Flash Boot diskette                | 83  |

| Using phlash.exe to re-program the flash chip | 84  |

| Appendix G: Carrier card design               | ٠.  |

| PrPMC connectors (Jn1 and Jn2)                | 85  |

| General                                       | 85  |

| Power                                         |     |

| PCI                                           | 85  |

| Jn1                                           | 86  |

| Clocking                                      | 86  |

| Arbitration                                   | 86  |

| Jn2                                           | 86  |

| Processor PMC                                 | 86  |

| RadiSys-defined PrPMC connector (Jn4)         | 86  |

| IDE                                           | 86  |

| Keyboard and mouse                            | 86  |

| Serial port                                   | 87  |

| Clocking                                      | 87  |

| Arbitration                                   | 87  |

| RTC battery                                   | 87  |

| Mechanical and thermal design                 | 87  |

| Power consumption                             | 87  |

| Airflow                                       | 87  |

| Maximum ambient temperature                   | 88  |

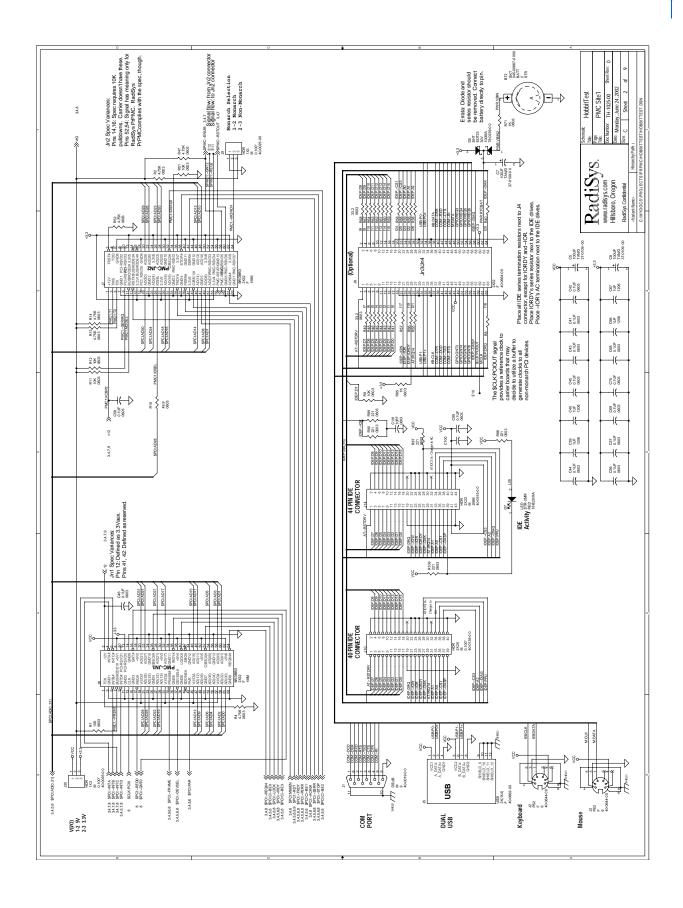

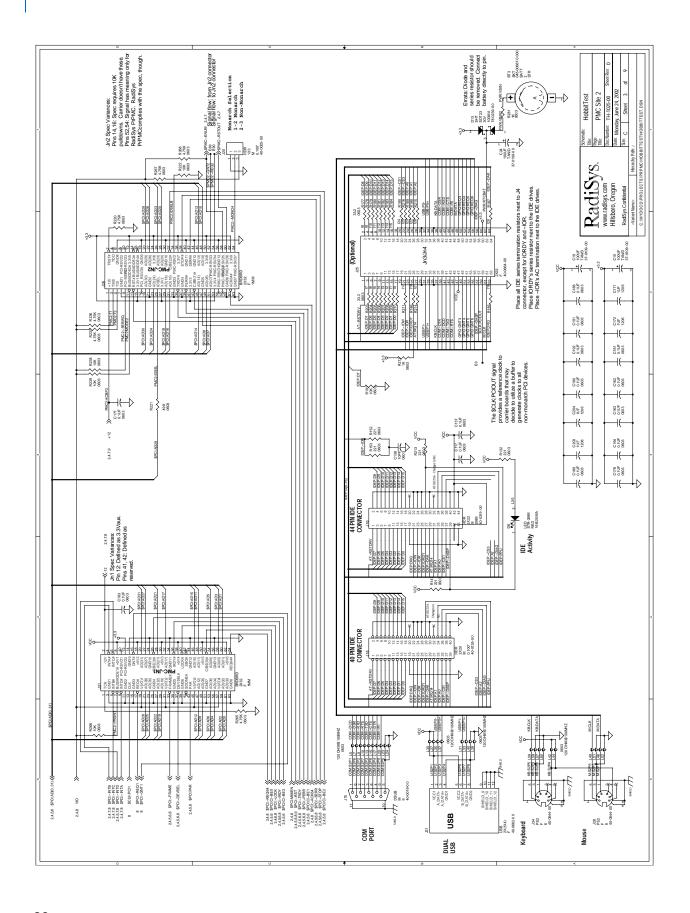

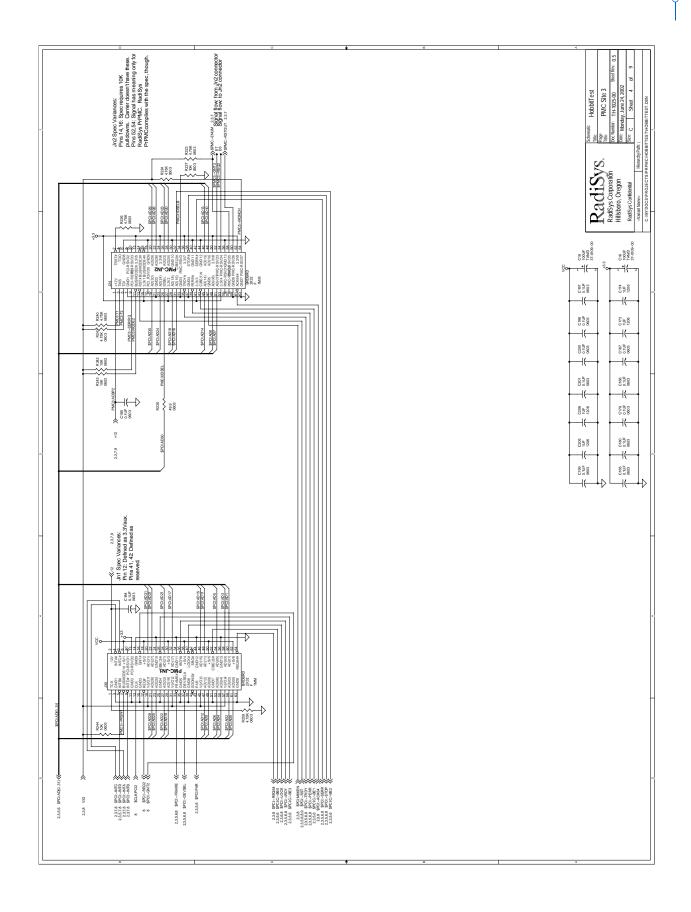

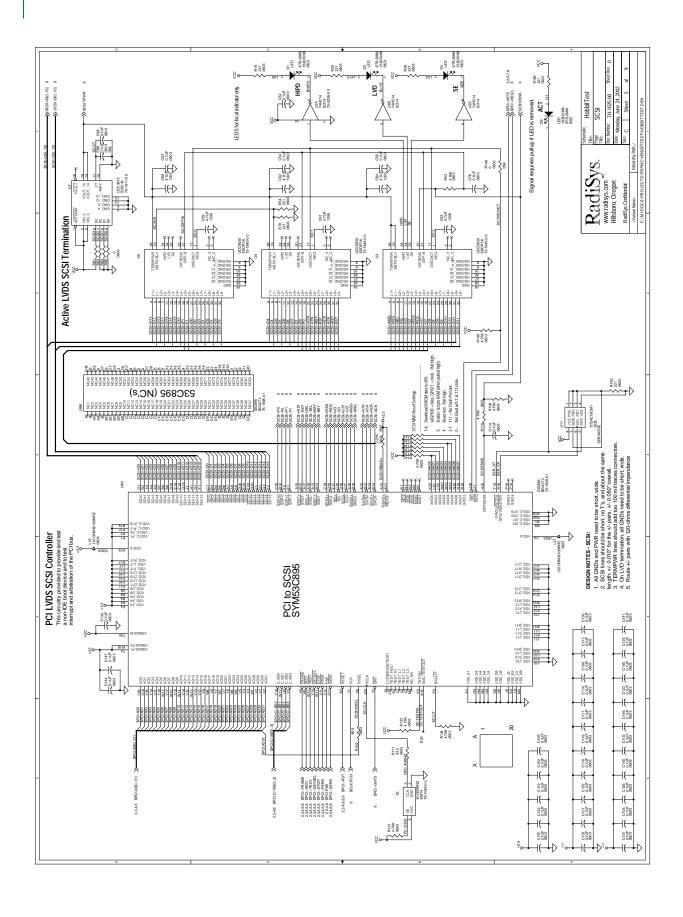

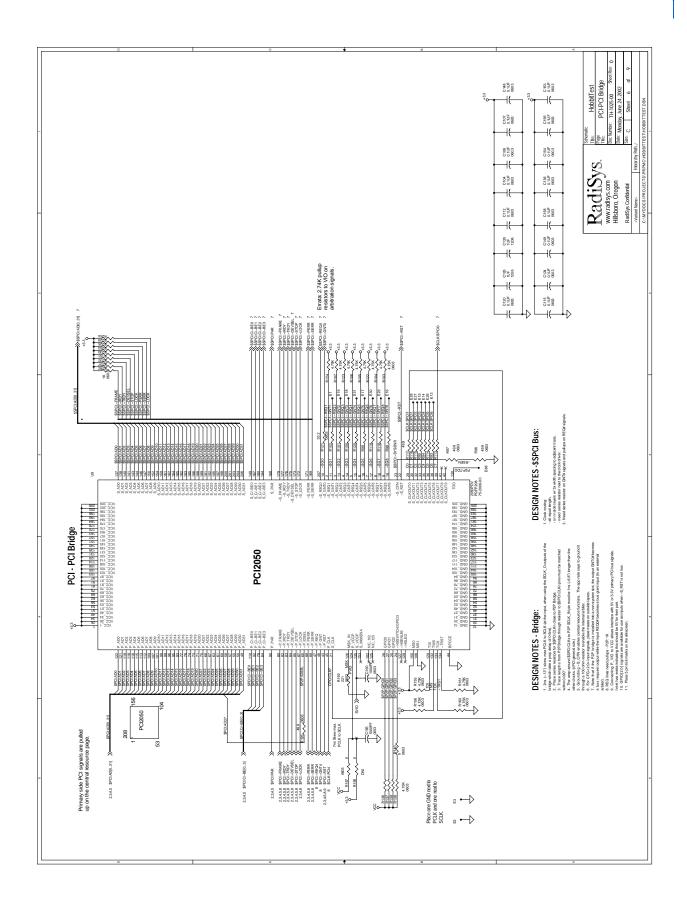

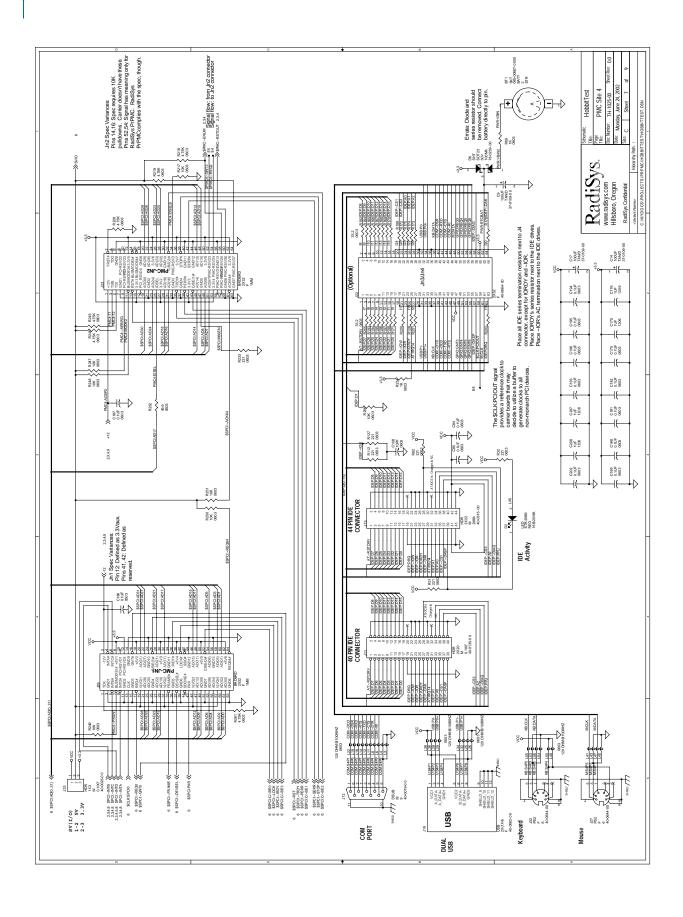

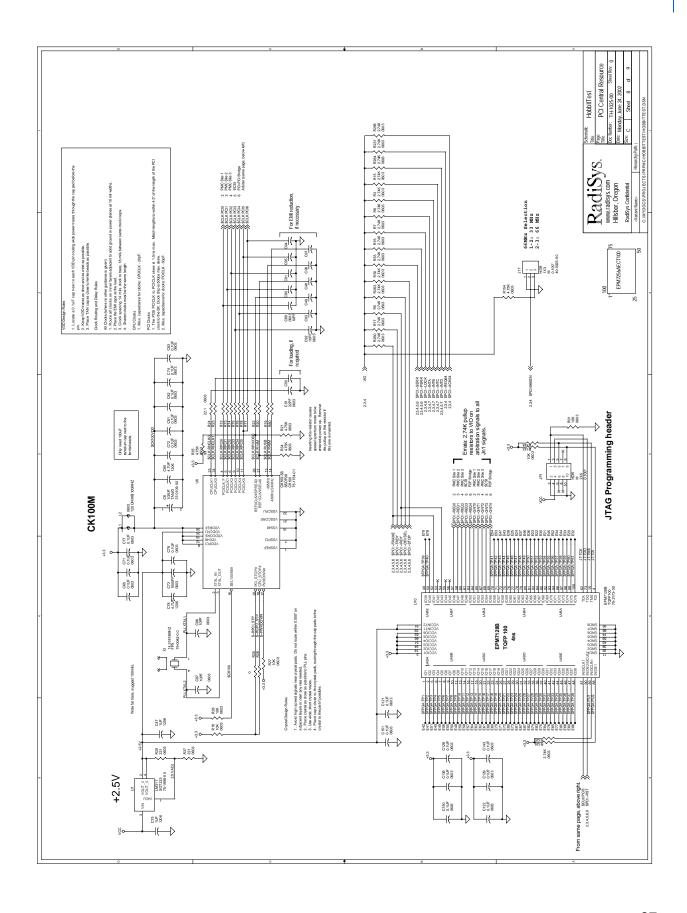

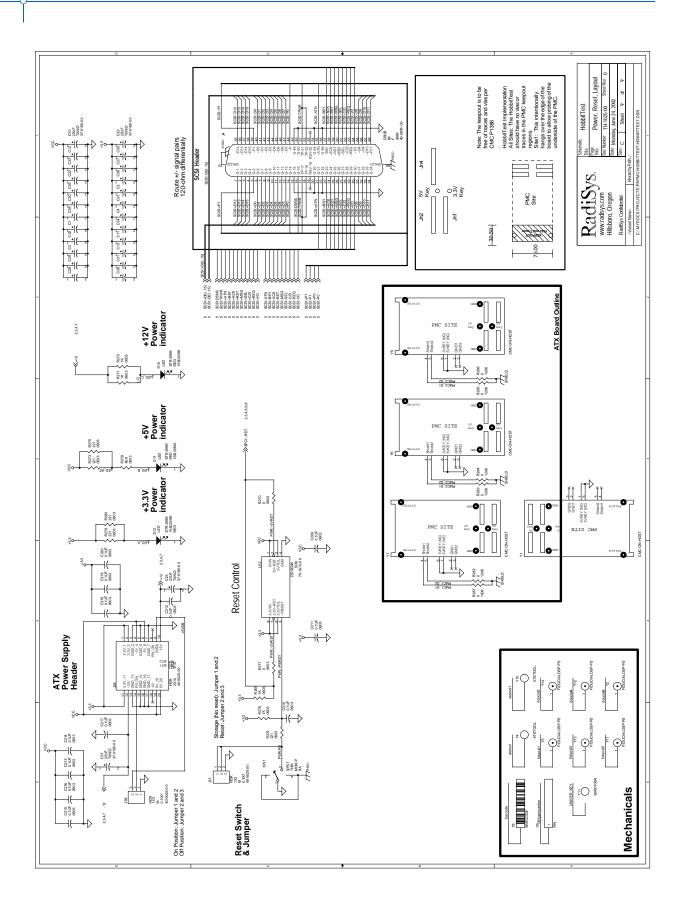

| Carrier card schematic samples                | 88  |

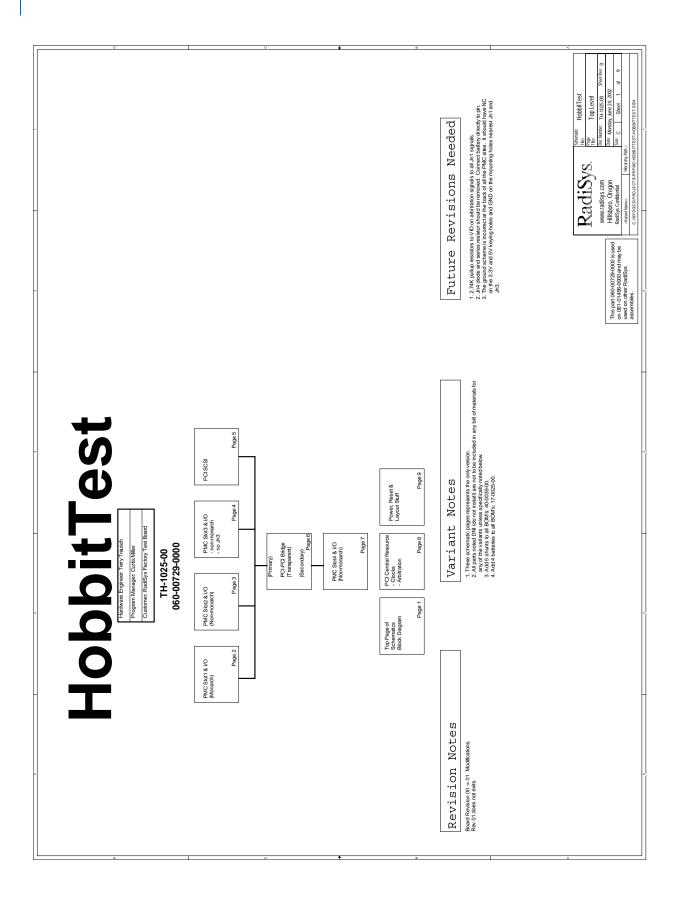

| Appendix H: EPC-6315 test board               |     |

| Features                                      | 99  |

| Specifications                                | 100 |

| Block diagram                                 |     |

| Physical interfaces                           |     |

| Connectors and jumpers                        |     |

| Reset switch                                  |     |

| Interrrupts                                   |     |

| Glossary                                      |     |

| •                                             |     |

| Index                                         | 111 |

# EPC®-6315 Hardware Reference

# Figures

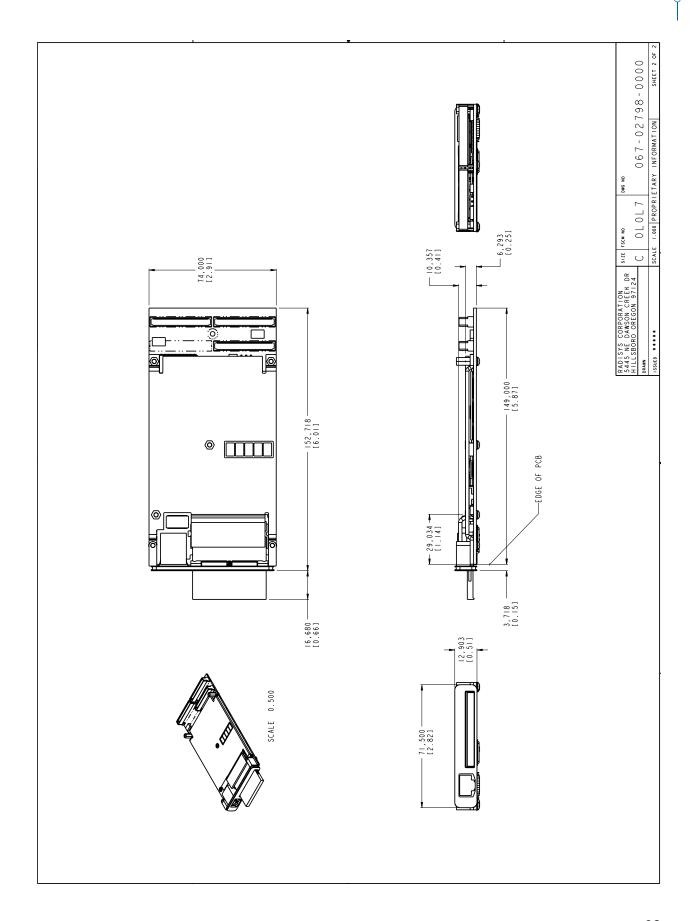

| Figure 1-1. The EPC-6315                                  | 1   |

|-----------------------------------------------------------|-----|

| Figure 2-1. Installing a PMC module                       | 8   |

| Figure 2-2. Separating a PMC module from the carrier card | 10  |

| Figure 4-1. BIOS Main Setup menu                          | 25  |

| Figure 4-2. Primary Master/Slave sub-menus                | 27  |

| Figure 4-3. Advanced menu                                 | 31  |

| Figure 4-4. PCI Configuration sub-menu                    | 33  |

| Figure 4-5. PrPMC customizations sub-menu                 | 34  |

| Figure 4-6. PCI/PNP ISA UMB Region Exclusion sub-menu     | 36  |

| Figure 4-7. PCI/PNP ISA IRQ Resource Exclusion sub-menu   | 37  |

| Figure 4-8. Cache Memory sub-menu                         | 38  |

| Figure 4-9. Console Redirection sub-menu                  | 43  |

| Figure 4-10. I/O Device Configuration sub-menu            | 45  |

| Figure 4-11. Boot menu                                    | 46  |

| Figure 4-12. Exit menu                                    | 48  |

| Figure 4-13. CMOS Save & Restore sub-menu                 | 49  |

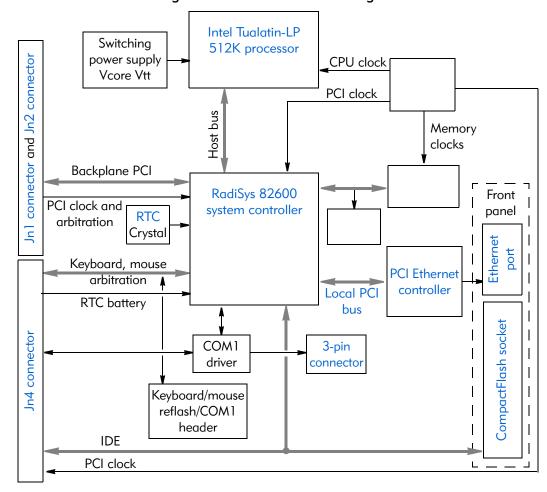

| Figure 5-1. EPC-6315: block diagram                       | 52  |

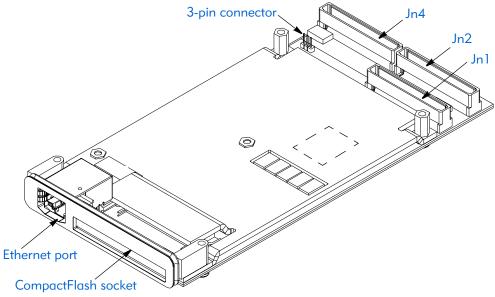

| Figure C-1. EPC-6315: connectors                          | 67  |

| Figure E-1. Flash chip memory addresses                   | 79  |

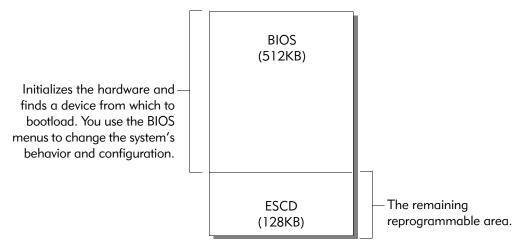

| Figure F-1. Flash chip configuration                      | 81  |

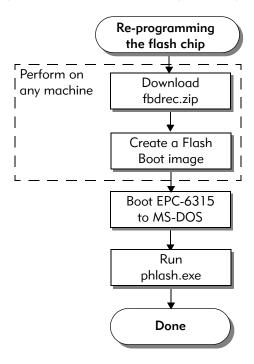

| Figure F-2. Flash chip re-programming process flow        | 82  |

| Figure H-1. Block diagram 1                               | 101 |

|                                                           |     |

| Tables                                                    |     |

| Γable 1-1. Environmental specifications                   | 4   |

| Γable 1-2. Additional EPC-6315 specifications             |     |

| Table 5-1. Power-up configuration settings                |     |

| Table 5-2. Memory map                                     | 56  |

| Table 5-3. PCI device configuration                       | 59  |

| Table 5-4. Power estimates                                | 61  |

| Гable B-1. Interrupts                                     | 65  |

| Гable C-1. CompactPCI J1 connector pin definitions        | 68  |

| Table C-2. Jn1 connector pin definitions                  | 69  |

| Table C-3. Jn2 connector pin definitions                  | 70  |

| Table C-4. Optional JN4 connector pin definitions         | 71  |

| Гable C-5. PMC connector Jn4 signal summary               | 72  |

| Table C-6. Ethernet pin definitions                       | 75  |

| Гable C-7. Compact Flash socket pin definitions           | 75  |

| Γable C-8. 3-pin connector pin definitions                | 76  |

| Table H-1. Environmental specifications 1                 |     |

| ±                                                         | 100 |

| Table H-2. Connector and jumper descriptions   1          |     |

# 1 Introduction

The EPC®-6315 PrPMC (Processor PCI Mezzanine Card) uses the RadiSys 82600 integrated chipset to bring an Intel Architecture processor into ultra-dense form factors. With the ability to accept a type I Compact Flash device, the EPC-6315 can be a completely self-standing processor in any application.

The EPC-6315 includes an 800MHz Pentium III processor with up to 512MB of on-board SDRAM. The EPC-6315 also features ECC protection of memory with single-error correction and double-error detection capability. Performance is maximized with the standard 133MHz PSB and 133MHz memory bus. For maximum flexibility, the EPC-6315 leverages the dual mode PCI-to-PCI bridge capability of the RadiSys 82600 to automatically configure the bridge based on the strapping of the slot on the baseboard. This capability allows the EPC-6315 to become a Monarch PrPMC, and provide PCI bus enumeration and service interrupts on the PCI bus or a non-Monarch PrPMC and function as a PCI-based auxiliary processor.

The Jn1 and Jn2 connectors provide a 32-bit 33/66MHz interface to the PCI bus on the baseboard as well as providing power and ground. The optional Jn4 connector provides a full set of I/O, which includes EIDE, COM, and keyboard/mouse interfaces. The front panel provides 10/100BASE-T Ethernet connector and Compact Flash socket.

Figure 1-1. The EPC-6315

You can order the EPC-6315 in these configurations:

| Configuration   | Description  | Memory IC capacity | No. IC chips |

|-----------------|--------------|--------------------|--------------|

| EPC6315-800-256 | 256 MB SDRAM | 32 Mb x 8          | 9            |

| EPC6315-800-512 | 512 MB SDRAM | 64 Mb x 8          | 9            |

### **Features**

The EPC-6315 includes:

### Compatibility

• Compatible with *Processor PMC standard*, VITA 32-199X, *Draft* 0.41

### Intel Tualatin LP processors in micro-FCBGA package

- 800 MHz core frequency.

- 133 MHz PSB (Processor Side Bus) frequency.

- 512 KB secondary (L2) cache.

- Switching power supply for CPU core voltage; linear supplies for interface voltages.

### **CPU** subsystem

RadiSys 82600 dual PCI embedded system controller:

For detailed information about the 82600 chip, see the 82600 High Integration Dual PCI System Controller Data Book.

- Dual independent PCI bus architecture.

- Monarch and non-Monarch capability on external PCI bus.

- Memory controller with direct BIOS flash support.

- Two 82C59 interrupt controllers.

- 82C54 timer/counter.

- 74LS612 address mapper.

- PS/2 compatible keyboard/mouse port.

- SMBus host interface.

- Two 82C37 DMA controllers.

- Real-time clock.

- COM port support with 16550 compatible UART.

- Integrated watchdog timer.

- Clock generator and SDRAM clock buffer supporting 133 MHz host clocks and PCI clocks.

- On-board memory capacity: up to 512 Mbytes of PC-133 compliant SDRAM.

- 32 Mb (4 MB) 3V Intel Strata Flash memory.

#### I/O

- Intel PCI Ethernet controller independently supporting 10BASE-T or 100BASE-TX.

- Compact Flash.

#### Connectors

- Carrier card

- Jn1 and Jn2 connectors

Provide a 32-bit 33/66 MHz interface to the PCI bus on the baseboard, plus provides a power and ground state compatible with the Processor PMC draft standard.

- Jn4 connector (optional)

Provides a full set of I/O, including EIDE, COM, and keyboard/mouse interfaces.

- 3-pin header Provides access to the system BIOS.

### Front panel

- RJ-45 connector.

- 10/100BASE-T Ethernet connector

To simplify network connections, this connector is available on the front panel.

- Compact flash socket

Accommodates a Type I compact flash card. With the ability to accept a

Type I Compact Flash device, the EPC-6315 can be a completely self standing processor in any application.

# **Specifications**

### **Environmental**

The EPC-6315 meets the following environmental specifications.

- The EPC-6315 is for use only with compatible UL listed computers that have installation instructions detailing user installation of card cage accessories.

- The operating environment must provide sufficient airflow (200 LFM) across the CPU board to keep it within its temperature specification. Failure to provide sufficient airflow may result in CPU failure.

The maximum temperature decreases when the relative humidity exceeds 30%.

Table 1-1. Environmental specifications

| Parameter                          | Conditions | Detailed specification                                                                 |

|------------------------------------|------------|----------------------------------------------------------------------------------------|

| Temperature (ambient)              | Operating  | +5°C to 50°C derated 2°C per 1000 ft (300 m) over 6600ft (2000m) with 200 LFM airflow. |

|                                    | Storage    | –20°C to +60°C.                                                                        |

| Relative humidity                  | Operating  | 20% to 90% non-condensing 20% per hour                                                 |

|                                    |            | maximum excursion gradient                                                             |

|                                    | Storage    | 5% - 95% non-condensing 20% per hour maximum excursion gradient.                       |

| EMC <sup>1</sup> radiated emission | Operating  | EN 55022:1998, Class B.                                                                |

| Conducted emissions                | Operating  | EN 55022:1998, Class B.                                                                |

| Vibration                          | Operating  | 0.04g <sup>2</sup> /Hz from 5 to1000 Hz random, 10 min per sweep cycle.                |

|                                    | Storage    | 0.04g <sup>2</sup> /Hz from 5 to1000 Hz random, 10 min per sweep cycle.                |

| Shock,                             | Operating  | 5g, 11ms, half-sine.                                                                   |

| (un-packaged)                      | Storage    | 15g, 11ms, half-sine.                                                                  |

| MTBF                               |            | 309,298 hours at 50°C using Bellcor Issue 6.                                           |

| Immunity                           |            |                                                                                        |

| ESD <sup>1</sup>                   | Operating  | (All performance criteria from IEC 1000-4-2/EN61000-4-2:1995):                         |

|                                    |            | 8KV direct contact, performance criteria B.                                            |

|                                    |            | 15 KV air discharge, performance criteria B.                                           |

| Radiated <sup>1</sup>              | Operating  | (Performance criteria A from IEC 1000-4-3/EN61000-4-3:1995).                           |

|                                    |            | Test Level 3V/m and 10V/m.                                                             |

| Surge                              | Operating  | (Performance criteria B from IEC 1000-4-4/EN61000-4-4:1995).                           |

|                                    |            | Test Level 0.5kV.                                                                      |

| Voltage dips and                   | Operating  | (From IEC 1000-4-11/EN61000-4-11:1995):                                                |

| interruptions                      |            | >95% dip, 10ms—Performance criteria B.                                                 |

|                                    |            | 30% dip, 500ms—Performance criteria C.                                                 |

|                                    |            | >95% dip, 5000ms—Performance criteria C.                                               |

| Conducted                          | Operating  | (Performance criteria A from IEC 1000-4-6/EN61000-4-6:1995).                           |

| Fast<br>transient/burst            | Operating  | (Performance criteria B from IEC 1000-4-4/EN61000-4-4:1995):                           |

| 1 = .                              |            | Test Level 0.5kV.                                                                      |

These are system level tests. Conformance of the product to these specifications may be affected by the complete system's ability to conform.

# Additional specifications

Table 1-2. Additional EPC-6315 specifications

| Characteristic | Value                            |                                                     |

|----------------|----------------------------------|-----------------------------------------------------|

| Mechanical     | Dimensions <sup>1</sup>          | 74.0 mm x 149.00 mm                                 |

|                | Height, component side           | е                                                   |

|                | First 31mm                       | 9.5mm                                               |

|                | Remainder                        | 4.7mm, maximum                                      |

|                | Height, solder side <sup>2</sup> | 3.5mm (this includes the 1.6mm board                |

|                |                                  | thickness)                                          |

|                | Thickness                        | 1.6 mm                                              |

|                | Component surface to             | 10 mm                                               |

|                | host component surfac            | e                                                   |

| Heat sink      | Provides sufficient cooli        | ng for the CPU when used in an environment          |

|                | providing 200 LFM airf           | low at a maximum temperature of $50^{\circ}$ C (air |

|                | coming into the chassis          | s). <sup>3</sup>                                    |

<sup>&</sup>lt;sup>1</sup> The mechanical outline of the PrPMC module conforms to the dimensions defined by a single wide, standard length PMC module.

$<sup>^{2}\,</sup>$  Measured from the component side for single slot CompactPCI use.

<sup>&</sup>lt;sup>3</sup> The customer assumes the responsibility for doing a detailed thermal analysis for the CPU board on this carrier.

2

# Configuration and installation

This chapter describes how to install an EPC-6315 PMC on a RadiSys EPC board.

| For information about                                | Go to this page |

|------------------------------------------------------|-----------------|

| Before you begin                                     | {               |

| Installing the EPC-6315 PMC on the carrier card      |                 |

| Maintaining and upgrading the EPC-6315               | 10              |

| Disconnecting the EPC-6315 PMC from the carrier card | 10              |

Avoid causing ESD (electrostatic discharge) damage by following these conventions:

- Keep the blade in its anti-static bag until you are ready to install it.

- Install the blade (as described later in this chapter) only in a static-free environment:

- Before touching the blade, attach an ESD wrist strap to your wrist and connect its other end to the ESD friction-lock connector at the shelf's lower left.

- Remove the blade from its antistatic bag only in a static-free environment.

- Avoid touching printed circuits, connector pins, and components. Where possible, hold the blade only by its edges or mounting hardware.

- Make the least possible movement with your body to minimize electrostatic charges created by contact with clothing fibers, carpet, and furniture.

- Keep one hand on the shelf, if possible, as you insert or remove a blade.

- Avoid placing the blade on the shelf cover or on a metal table. The cover and metal table increase the risk of damage because they provide an electrical path from your body through the blade.

The EPC-6315, like most other electronic devices, is susceptible to ESD damage. ESD damage is not always immediately obvious. It can cause a partial breakdown in semiconductor devices that might not result in immediate failure.

# Before you begin

The EPC-6315 requires a PMC carrier.

# Installing the EPC-6315 PMC on the carrier card

You install the EPC-6315 PMC on the carrier card as shown below.

Figure 2-1. Installing a PMC module

To install a PMC module:

- 1. Remove and save any blank faceplate from the PMC slot in the carrier card faceplate.

- 2. Position the PMC bezel through the PMC slot on the front panel.

- 3. Push the rear connectors into the carrier card.

- 4. Insert and tighten the screws on the back of the carrier card.

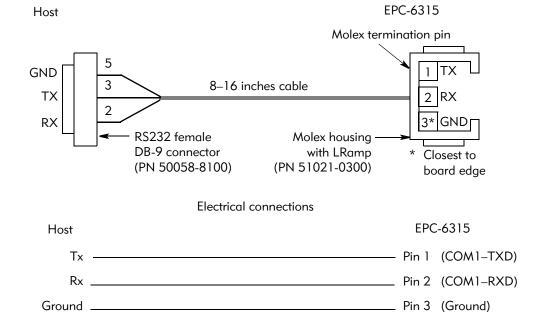

## Using the 3-pin connector

The EPC-6315 includes a 3-pin connector that you can use to access some COM1 signals.

Before you begin, ensure that you have a null-modem cable that connects the 3-pin connector to your terminal.

You must construct this cable; RadiSys does not supply a cable for the 3-pin connector. For pinout information, see 3-pin connector on page 76.

To use the 3-pin connector:

- 1. Attach the cable to the 3-pin connector and your terminal.

- 2. Start a terminal emulation program, such as Hyperterm or Telix, using these settings:

Baud rate: 115200

Parity: None

Data bits: 8

Stop bits: 1

Flow control: None

You can now access the BIOS setup program using the methods described in *Chapter 4*, *BIOS configuration*.

# Maintaining and upgrading the EPC-6315

Occasionally you will want to perform maintenance or upgrades on the EPC-6315. When this occurs, you must remove the board from the carrier card, repair or install the desired option, then re-install the board on the carrier card. The following section describes how.

# Disconnecting the EPC-6315 PMC from the carrier card

To separate the EPC-6315 from the carrier card:

Figure 2-2. Separating a PMC module from the carrier card

- 1. Remove screws on the back of the carrier card.

- 2. Pull the boards apart while keeping them parallel. Continue applying force until the connectors completely disengage.

After performing maintenance and/or upgrades, replace the EPC-6315 as described in *Installing the EPC-6315 PMC on the carrier card* on page 8.

# 3

# **Operating System Installation**

This document explains how to install Linux and VxWorks operating Ssstems on the EPC-6315.

- For MV Linux LSPs, contact MontaVista at this URL: http://www.mvista.com

- For VxWorks BSPs, contact RadiSys or WindRiver http://www.windriver.com http://www.radisys.com

###

# **Installing Red Hat Linux**

You can install Red Hat using either of these methods:

- Install Red Hat on a separate computer..

- Install Red Hat over the serial port.

The following sections describe how.

## Installing Red Hat on a separate computer

To install Red Hat, use a separate computer with a VGA card and prepare a hard drive for transfer to the EPC-6315:

- 1. Install a hard drive and CD-ROM drive in a PC with a VGA card. Ensure that the hard drive is the master on the primary cable.

- 2. Power on the system, insert the Red Hat bootable CD, and install Linux with the configuration you desire.

- 3. Reboot the system and log in at the Linux command prompt as "root".

4. Configure Linux for serial redirection. Using any editor, change these files:

| File           | Instructions                                                        |

|----------------|---------------------------------------------------------------------|

| /etc/inittab   | 1. Change the first TTY configuration line to read:                 |

|                | 1: 2345:respawn:/sbin/mingetty ttyS0 115200 vt100                   |

|                | 2. Comment out the remaining TTY configuration lines.               |

|                | 3. Save your changes.                                               |

| /etc/securetty | 1. Add this line at the bottom of the file:                         |

|                | ttyS0                                                               |

|                | This file lists TTYs that allow logins. Adding the above line       |

|                | allows you to log in as root over the serial port.                  |

|                | 2. Save your changes.                                               |

| /etc/lilo.conf | 1. In your kernel entry, add a kernel "append" parameter similar    |

|                | to this example:                                                    |

|                | <pre>image="/boot/vmlinuz-2.4.7-10"</pre>                           |

|                | label="linux"                                                       |

|                | read-only<br>root="/dev/hda1"                                       |

|                | append = "console=ttyS0,115200n8"                                   |

|                | Adding this parameter to the kernel instructs it to redirect kernel |

|                | messages to the serial port.                                        |

|                | 2. Save your changes.                                               |

5. Write changes to the master boot record by entering this command at the command prompt:

lilo

- 6. Shut down the system.

- 7. Transfer the hard drive to the EPC-6315.

- 8. Boot the EPC-6315.

You can now log in over the serial port as root.

# Installing Red Hat 7.3 or later over the serial port

Red Hat 7.3 already contains the correct TTY settings. This allows you to install Linux on the EPC-6315 without transferring the hard drive from another system. To install Red Hat 7.3 over the serial port:

- 1. Attach a hard drive and CD on an IDE cable, setting the hard drive to master and the CDROM to slave.

- 2. Power on the EPC-6315 system and immediately insert the Red Hat bootable CD-ROM.

- 3. Modify the BIOS settings to boot the EPC-6315 from the CD-ROM:

- A. Press F2 to enter the BIOS Setup program (see page 23).

- B. Make the CD-ROM the first device the EPC-6315 tries to boot from by moving the CD-ROM to the top of the list in the Boot menu (see page 46).

- C. Change the console and terminal baud rates to 9600.

- D. Press F10 to save your changes, then reboot.

The system boots over the serial port at 9600 bps, then displays the boot: prompt.

4. Enter this command:

```

linux console=ttyS0,9600n8

```

The serial port displays kernel messages.

5. Follow the instructions, configuring Linux to your liking. When prompted for kernel parameters, enter:

```

console=ttyS0,9600n8

```

Finish the installation and reboot the system. The serial port displays a login prompt at 9600 bps.

- 6. Log in as root.

- 7. To change the console baud rate to 115200, edit these files:

| File           | Instructions                                                                                                                   |

|----------------|--------------------------------------------------------------------------------------------------------------------------------|

| /etc/inittab   | 1. Change the first TTY configuration line to read:                                                                            |

|                | <ol> <li>2345:respawn:/sbin/mingetty ttyS0 115200 vt100</li> <li>Comment out the remaining TTY configuration lines.</li> </ol> |

|                | 3. Save your changes.                                                                                                          |

| /etc/lilo.conf | <ol> <li>In your kernel entry, add a kernel "append" parameter similar<br/>to this example:</li> </ol>                         |

|                | <pre>image="/boot/vmlinuz-2.4.7-10"     label="linux"     read-only</pre>                                                      |

|                | <pre>root="/dev/hda1" append = "console=ttyS0,115200n8" 2. Save your changes.</pre>                                            |

8. Write the changes to the master boot record by entering this command at the command prompt:

lilo

- 9. Reboot the system.

- 10. Change the baud rate:

- A. During reboot, press F2 to enter the BIOS Setup program (see page 23).

- B. Change the console and terminal baud rates to 115200 bps.

- C. Press F10 to save each change.

The system boots over the serial port at 115200 bps, then displays the Linums login prompt.

## Installing MontaVista Linux

This section explains how to network boot MontaVista Linux from the RadiSys-supplied LSP.

### Configure the host to boot EPC-6315 over the network

The following sections provide instructions on how to configure the different components of the host system. These instructions are for only Linux hosts running Red Hat 7.3 or later.

### Extract the kernel source and filesystem

- 1. Obtain the MontaVista Linux host tools from MontaVista (www.mvista.com).

- 2. Install the tools according to the host tools instructions. When the installation prompts you to install an LSP, choose any LSP based on an Intel Pentium III processor.

- 3. Extract kernel source files from the RadiSys-supplied LSP archive to a work area.

### Configure DHCP

Ensure that the DHCP server is configured correctly. An incorrect configuration may cause problems for other machines on your network.

To configure DHCP as root:

1. Make sure a DHCP server is installed and that the following file exists:

| Version     | Filename                   |

|-------------|----------------------------|

| Red Hat 7.x | /var/lib/dhcp/dhcpd.leases |

If the file does not exist, create an empty one using the Unix touch command:

| Operating system | Command                          |

|------------------|----------------------------------|

| Red Hat 7.x      | touch /var/lib/dhcp/dhcpd.leases |

- 2. Edit the DHCP daemon configuration file:

- A. Add the following configuration into your /etc/dhcpd.conf file:

```

allow booting;

allow booting;

subnet SubAddress netmask NetAddress {

default-lease-time 1209600; # two weeks

max-lease-time 31557600; # one year

group {

next-server TFTPAddress;

option routers Gateway;

host Target {

hardware ethernet MACAddress;

fixed-address IPAddress;

option root-path "/opt/mvlcge/devkit/x86/pentium3/target";

filename "bzImage.nb.mba";

}

}

```

}

### B. Change the value of these parameters:

SubAddress The subnet address, consisting of four numbers from 0–255

separated by dots (periods).

NetAddress The netmask address, consisting of four numbers from 0–255

separated by dots (periods).

TFTPAddress The TFTP server address, consisting of four numbers from

0–255 separated by dots (periods).

Gateway The router or gateway address, consisting of four numbers

from 0–255 separated by dots (periods).

Target The target name, consisting of three sections separated by

dots (periods). For example:

test1.mvista.com

This name must be consistent with the host name used for

DNS or host file look-up.

MACAddress The target MAC (Ethernet) address, consisting of six 2-digit

numbers separated by colons:

xx:xx:xx:xx:xx

The MAC address typically looks like this:

00:00:50:xx:xx:xx

The target's IP address, consisting of four numbers from 0–255 separated by dots (periods).

3. Restart dhepd by entering this command:

/etc/rc.d/init.d/dhcpd restart

The DHCP daemon is required to service BOOTP requests when booting the target. To run the DHCP daemon (on the host) on every boot, enter this command:

chkconfig dhcpd on

Use caution when running this command on a corporate network. Your DHCP server may interfere with the corporate DHCP server.

DHCP is now configured.

### **Configure TFTP**

To configure TFTP, follow the instructions for the host you are using. The following instructions use the version of TFTP distributed with CGE.

Some host distributions do not have the most recent version of TFTP and some versions of TFTP do not work correctly with CGE. For that reason, MontaVista Software distributes a version of TFTP with CGE, installed by default at /opt/mvlcqe/host/bin.

#### Red Hat 7.x

To configure TFTP on a Red Hat 7.x host as root:

1. Create (or edit) the file /etc/xinetd.d/tftp. Use the following format:

```

#/etc/xinetd.d/tftp

service tftp

{

socket_type = dgram

wait = yes

user = root

log_on_success += USERID

log_on_failure += USERID

server = /opt/mvlcge/host/bin/in.tftpd

server_args = -r blksize /tftpboot

disable = no

protocol = udp

}

```

2. Ensure that the /tftpboot directory exists. To create the directory, enter this command:

```

mkdir /tftpboot

```

3. Have xinetd re-read its configuration file by entering this command:

```

/etc/rc.d/init.d/xinetd restart

```

4. Stop any any TFTP daemons that have not timed out by entering this command:

```

killall in.tftpd

```

### Configure NFS

To configure NFS as root:

1. Add this line in /etc/exports:

```

/opt/mvlcge/devkit/x86/pentium3/target *(rw,no root squash,no all squash)

```

2. Stop, then start, the NFS daemon by entering these command:

```

/etc/rc.d/init.d/nfs stop

/etc/rc.d/init.d/nfs start

```

3. Set the NFS daemon to run during every boot by entering this command:

```

/sbin/chkconfig nfs on

```

4. Synchronize the NFS daemon by entering this command:

```

/usr/sbin/exportfs -ra

```

NFS is now configured.

### Network boot the kernel

To network boot a kernel on the EPC-6315:

- 1. Change to the working folder (directory) where you placed the kernel sources.

- 2. Build the kernel by entering these commands:

```

make clean; make dep; make bzImage

```

- 3. Apply network boot headers to the kernel image by copying bzImage to /tftpboot.

- 4. Change the boot device:

- A. Attach:

- An Ethernet cable to the EPC-6315 that allows access to your DHCP server.

- A null modem cable from the EPC-6315 to a PC serial port.

- B. Open a terminal, such as minicom, and set the communications parameters to:

Baud rate: 115200

Parity: None

Data bits: 8

Stop bits: 1

Flow control: None

- C. Power-on the EPC-6315.

- D. Enter the BIOS and set the first boot device as UNDI (on-board Ethernet). Press F10 to save and reboot. The kernel boots over the network and displays on the serial port.

- 5. Log in as root.

### Install MontaVista Linux to a hard drive

Creating a bootable hard drive or CompactFlash requires that you network boot a kernel and NFS a filesystem, as described in the previous section. You then attach a bootable media device, prepare a filesystem on it, and copy the filesystem over NFS.

- 1. Prepare the bootable media:

- A. Attach a CompactFlash into the front panel slot or attach an IDE hard drive to the IDE connector on your baseboard. Be sure that the hard drive is set up as the master.

- B. Network boot the system over the serial port at 115200 bps.

- C. Run fdisk:

- i. Create partitions on the drive by entering this command:

fdisk /dev/hda

- ii. Create at least one partition to use as /root.

- iii. Tag the partition with ID 83, using the t command.

- iv. Mark it bootable by using the a command.

- v. Save your changes by entering w.

For more information about fdisk, see the HOWTOs on using fdisk, available on the web.

You can find out more about fdisk at www.redhat.com. To locate the utility, search for fdisk on the site.

- 2. Prepare a filesystem:

- A. Create a filesystem by entering this command:

```

mkfs-ext2 /dev/hda1

```

B. Mount the filesystem to /mnt by entering this command:

```

mount /dev/hda1 /mnt

```

C. Copy the filesystem from NFS to the mount point /mnt by entering these commands:

```

cp -aR /bin /mnt

cp -aR /boot /mnt

cp -aR /dev /mnt

cp -aR /etc /mnt

cp -aR /home /mnt

cp -aR /lib /mnt

cp -aR /opt /mnt

cp -aR /root /mnt

cp -aR /sbin /mnt

cp -aR /tmp /mnt

cp -aR /usr /mnt

cp -aR /var /mnt

mkdir /mnt/mnt

mkdir /mnt/proc

```

- 3. On your host, copy the bzImage kernel you created (in step 2 of *Network boot the kernel* on page 16) to /root. On the EPC-6315 terminal, copy this image to /mnt/boot.

- 4. Change the current /root to the mounted drive by entering this command:

```

chroot /mnt

```

5. Configure Linux for serial redirection. Using any editor, change this file:

| File           | Instructions                                                  |

|----------------|---------------------------------------------------------------|

| /etc/lilo.conf | 1. Revise the file similar to this example, paying particular |

|                | attention to the tty settings:                                |

|                | timeout="50"                                                  |

|                | default="MVL CGE 2.1"                                         |

|                | boot=/dev/hda                                                 |

|                | map=/boot/map                                                 |

|                | install=/boot/boot.b                                          |

|                | append="console=ttyS0,115200n8"                               |

|                | lba32                                                         |

|                | <pre>image="/boot/bzImage"</pre>                              |

|                | label="MVL CGE 2.1"                                           |

|                | read-only                                                     |

|                | root=/dev/hda1                                                |

|                | 2. Save your changes.                                         |

6. Write the changes to the master boot record by entering this command at the command prompt:

lilo

- 7. Reboot the system.

- A. Press F2 to enter the BIOS Setup program (see page 23).

- B. Change the first boot device to be the bootable drive.

- C. Press F10 to save and reboot.

You should now boot from CompactFlash or the hard drive with a serial console.

# Installing VxWorks

This section explains how to install VxWorks on a blank CompactFlash or hard drive

## Requirements

To install a VxWorks BSP on an EPC-6315 you will need:

- The EPC-6315 VxWorks BSP from RadiSys. You can request it from RadiSys by sending email to <a href="mailto:support@radisys.com">support@radisys.com</a>.

- A DOS boot disk with fdisk and format utilities.

- Two DOS-formatted floppy diskettes.

- A 10MB or greater CompactFlash or hard drive.

- A CF-to-IDE (standard hard drive connector) adapter (needed only if you plan to install VxWorks on CompactFlash).

### Installation

- 1. Install the BSP:

- A. Obtain the RadiSys EPC-6315 VxWorks BSP from RadiSys. You can request it from support@radisys.com.

- B. Install the BSP by extracting the archive and running setup.exe.

- 2. Build projects:

- A. In the Tornado environment, create a project based on the EPC6315 BSP.

- B. Build bootrom\_uncmp and vxWorks.st.

For more information about creating and building files, see your VxWorks documentation.

- 3. Create a boot disk with the VxWorks bootloader:

- A. Insert a formatted floppy into your disk drive.

- B. In a DOS box, change to the directory where bootrom\_uncmp resides.

- C. Create a bootable floppy by entering this command:

```

mkboot a: bootrom uncmp

```

- D. Copy the vxsys.com file to the floppy diskette. Typically, this file resides at c:\tornado\host\x86-win32\bin\

- E. Copy the VxWorks.st image to the boot floppy by entering:

```

copy vxWorks.st a:

```

If this file does not fit on the boot floppy, copy vxWorks.st to a different floppy.

- F. Label this as the EPC-6315 bootdisk.

- 4. Prepare the device to be the boot device:

- A. On a separate computer, install the HD or CF card as drive C (i.e., Master drive on primary IDE cable for a HD, to install to CF a CF-to-IDE adapter must be used). The HD or CF must be the first drive and, when formatted, be recognized in DOS as drive C.

- B. Boot the PC from a DOS boot disk.

- C. Run fdisk and create a bootable FAT filesystem and restart the system.

- D. When the DOS prompt displays, enter this command:

```

format c:

```

E. Remove the DOS disk and insert the VxWorks bootdisk.

5. Make a VxWorks-bootable hard drive or CompactFlash by entering these commands:

| Command             | Description                                            |

|---------------------|--------------------------------------------------------|

| vxsys c:            | Installs the master boot record and initial bootloader |

| copy bootrom.sys c: | Copies the VxWorks bootloader to the drive.            |

| copy vxWorks.st c:  | Copies VxWorks image to the drive.                     |

- 6. Install the device in the system:

- A. Power down the system and remove the hard drive or CompactFlash card.

- B. Transfer the drive to the EPC-6315 system.

- 7. Start VxWorks:

- A. Boot the EPC-6315 system.

The default is to boot from "ata0", which is the CompactFlash card or master hard drive.

When the bootloader (bootrom\_uncmp) runs, a countdown displays.

B. Press a key to display a prompt, then enter c to configure your system. Set IP information to the values you desire.

To have VxWorks automatically initialize the on-board Ethernet, enter fei into the "other" field.

After you enter the parameters, the configuration is saved automatically to flash.

C. Boot VxWorks by entering @.

# **BIOS** configuration

The EPC-6315 uses the Phoenix NuBIOS to configure and select various system options. This chapter details the various menus and sub-menus used to configure the system. This chapter is written as though you are setting up each field in sequence and for the first time. Your system may be correctly pre-configured and require very little setup.

To revert to the original BIOS settings, select Load Setup Defaults from the *Exit* menu on page 48. This restores the original BIOS settings.

You may see some error messages during the execution of the BIOS initialization sequence. If errors occur during the POST (Power-On Self-Test), the BIOS displays the error on the appropriate line of the screen display and, depending on how your system is configured, either pauses or tries to continue. For information about error messages, see *Appendix D*, *Error messages*.

Pressing the Escape key during POST displays the Boot-First pop-up menu after POST completes. You can use this menu to override, for only this boot, the boot options. This menu includes the same options as the Boot Menu's top level. For information about the options, see *Boot menu* on page 46.

# **BIOS** setup screens

The EPC-6315's BIOS includes a setup program that displays and modifies the system configuration. The EPC-6315's nonvolatile CMOS RAM stores configuration information, and the BIOS uses it to initialize the EPC-6315 hardware.

You can enter the BIOS Setup only during the system reset process, following a power-up, front panel reset, or equivalent. To enter Setup, press the F2 key when prompted.

To view BIOS setup screens, the EPC-6315 must be attached to a terminal. For information about attaching to a terminal, see *Using the 3-pin connector* on page 9.

## Menu map

You set up the BIOS by making selections from the menus shown in the next table.

When reading this file online, you can immediately view information about any menu by placing the mouse cursor over menu name and clicking:

| Menu            | Sub-menu                                    |

|-----------------|---------------------------------------------|

| Main Setup menu | Primary Master/Slave sub-menus              |

| Advanced menu   | PCI Configuration sub-menu                  |

|                 | PrPMC customizations sub-menu               |

|                 | PCI/PNP ISA UMB Region Exclusion sub-menu   |

|                 | PCI/PNP ISA IRQ Resource Exclusion sub-menu |

|                 | Cache Memory sub-menu                       |

|                 | Console Redirection sub-menu                |

|                 | I/O Device Configuration sub-menu           |

| Boot menu       | None                                        |

| Exit menu       | CMOS Save & Restore sub-menu                |

# **Navigation**

| То                                                    | Do                                                                                                                                                                                        |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Display a menu                                        | Press the left or right cursor (arrow) keys and press the Enter key. If you use the arrow keys to leave a menu and then return, your active field is always at the beginning of the menu. |

| Display a submenu<br>(fields with a triangle at left) | Move the cursor to a field with a triangle and press the Enter key. If you select a sub-menu and then return to the main menu, the active field is that sub-menu heading.                 |

| Select a field                                        | Press the up or down cursor (arrow) keys                                                                                                                                                  |

| Select an option                                      | <ul> <li>Do one of these:</li> <li>Press the + and – keys to rotate through available options.</li> <li>In certain numeric fields, simply enter the desired number.</li> </ul>            |

The remainder of this chapter describes the fields in each menu and sub-menu. Additional help information is available in the help area on the Setup screen.

# Main Setup menu

ESC

Exit

←→ Select Menu

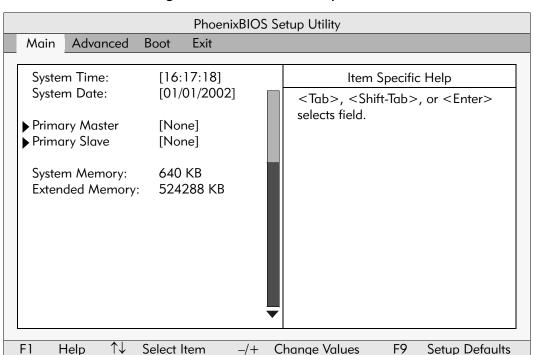

Figure 4-1. BIOS Main Setup menu

The far right menu in the menu bar is the Exit Menu. Use the options in the Exit menu to save your changes, re-load default BIOS settings, and so on. Press the ESC key to go immediately to the Exit Menu.

Enter Select ▶ Sub-Menu F10 Save and Exit

The fields in each menu and sub-menu are explained below. Additional help information is available in the help area on the BIOS setup screen.

| Field                   | Description                                                                                                                                                                                     |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Time/System Date | Sets the system time and date. To change these values, go to each field and enter the desired value. Press the tab key to move from hour to minute to second, or from month to day to year.     |

|                         | The default system time is 00:00; the default date is 01/01/1998.                                                                                                                               |

| Primary Master sub-menu | Displays a menu that you use to enter information for the master IDE drive connected to the primary IDE controller. For more information, see <i>Primary Master/Slave sub-menus</i> on page 27. |

| Primary Slave sub-menu  | Displays a menu that you use to enter information for the slave IDE drive connected to the primary IDE controller. For more information, see <i>Primary Master/Slave sub-menus</i> on page 27.  |

# EPC®-6315 Hardware Reference

| Field                 | Description                                                                                                                               |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Boot Options sub-menu | Displays a menu that you use to specify the PC's behavior during the boot process. For more information, see <i>Boot menu</i> on page 46. |

| System memory         | Displays the amount of conventional memory (below 1MB). This field is not editable; no user interaction is required.                      |

| Extended memory       | Displays the amount of extended memory (above 1MB). This field is not editable; no user interaction is required.                          |

## Primary Master/Slave sub-menus

There are two IDE adapter sub-menus for the primary hard disk controllers: a master and slave drive menu.

Access this screen to:

- See or reconfigure the detailed characteristics of the primary hard disk (select the IDE Adapter 0 Master item from the Main BIOS Setup).

- Set up new disks and allow the Setup program to determine the proper settings based on information on the disk. Note that the Setup program can detect these settings only on drives that comply with ANSI specifications.

- Set up existing (formatted) disks. Note that you must use the same parameters used when the disk originally was formatted. You must select an option for the Type field, then enter the specific cylinder, head, and sector information listed on the label attached to the drive at the factory.

Figure 4-2. Primary Master/Slave sub-menus

| PhoenixBIOS Setup Utility                                                      |                                                   |                                                        |                        |  |

|--------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------|------------------------|--|

| Main                                                                           |                                                   |                                                        |                        |  |

| Primary Master [Prim                                                           | ary Master]                                       | Item Spe                                               | ecific Help            |  |

| System Time: [16:                                                              | 17:18]                                            | <tab>, <shift-ta<br>selects field.</shift-ta<br></tab> | b>, or <enter></enter> |  |

| Cylinders: [4<br>Heads: [<br>Sectors: [3                                       | Auto]<br>190]<br>8]<br>32]<br>4MB                 |                                                        |                        |  |

| LBA Mode Control: [D<br>Transfer Mode: [Fo                                     | Disabled]<br>Disabled]<br>Tast PIO1]<br>Disabled] |                                                        |                        |  |

| F1 Help $\uparrow \downarrow$ Select I ESC Exit $\longleftrightarrow$ Select I |                                                   | hange Values Felect Sub-Menu F                         |                        |  |

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Туре      | Identifies the disk type. You can select one of these:                                                                                                                                                                                                                                                                                                                                                     |  |  |

|           | <ul> <li>Auto (default): Select this option when you want the<br/>POST to query the hard disk for its parameters whenever<br/>the POST runs. RadiSys recommends this option.</li> <li>Note: If you set a hard disk to "Auto", but no hard disk is<br/>actually present, the BIOS queries the (non-existent) hard<br/>disk until it times out, slightly increasing the duration of<br/>the POST.</li> </ul> |  |  |

|           | <ul> <li>None: Select this option if yours is not an IDE hard disk drive.</li> </ul>                                                                                                                                                                                                                                                                                                                       |  |  |

|           | <ul> <li>User: Select this option if you have an IDE disk but cannot employ the "Autotype" feature. Then enter the correct drive values for cylinders, heads, sectors/track, and write precompensation.</li> <li>ATAPI Removable: Select this option if you have a removable disk drive.</li> </ul>                                                                                                        |  |  |

|           | IDE Removable: Provides support for high-capacity disks that can be formatted as floppy or hard disks. This option may be used for compact flash cards.                                                                                                                                                                                                                                                    |  |  |

|           | <ul> <li>CD-ROM: Select this option if you have a CD-ROM drive.</li> </ul>                                                                                                                                                                                                                                                                                                                                 |  |  |

|           | <ul> <li>1–39: Select this option to specify a pre-determined<br/>hard-disk drive type. These drive types, found in the<br/>FDPT (Fixed Disk Parameter Table), are seldom used.<br/>RadiSys recommends that you avoid using this option.</li> </ul>                                                                                                                                                        |  |  |

|           | Note: For disks not supplied, consult the product documentation.                                                                                                                                                                                                                                                                                                                                           |  |  |

|           | When finished, press the ESC key to return to the <i>Main</i>                                                                                                                                                                                                                                                                                                                                              |  |  |

|           | Setup menu.                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Cylinders | Specifies the number of cylinders on this system. You can specify a number from 1 to 16.                                                                                                                                                                                                                                                                                                                   |  |  |

|           | <b>Note</b> : This field displays only when the Type field contains a value of [User] or [1–39]. You can edit this field only when the Type field contains a value of [User].                                                                                                                                                                                                                              |  |  |

| Heads     | Specifies the number of heads on this system.                                                                                                                                                                                                                                                                                                                                                              |  |  |

|           | <b>Note</b> : This field displays only when the Type field contains a value of [User] or [1–39]. You can edit this field only when the Type field contains a value of [User].                                                                                                                                                                                                                              |  |  |

| Sectors   | Specifies the number of sectors in each track on this system.                                                                                                                                                                                                                                                                                                                                              |  |  |

|           | <b>Note</b> : This field displays only when the Type field contains a value of [User] or [1–39]. You can edit this field only when the Type field contains a value of [User].                                                                                                                                                                                                                              |  |  |

| Field                  | Description                                                                                                                                                                                                                                                                                               |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Multi-Sector Transfers | Allows the System BIOS to read ahead by the specified number of sectors during disk access. This has the effect of reading more data at once to reduce the absolute number of discrete disk reads performed by the operating system, which may increase system performance.  You can select one of these: |

|                        | Disabled (default if no drive is installed)                                                                                                                                                                                                                                                               |

|                        | • 2 Sectors                                                                                                                                                                                                                                                                                               |

|                        | • 4 Sectors                                                                                                                                                                                                                                                                                               |

|                        | • 8 Sectors                                                                                                                                                                                                                                                                                               |

|                        | <ul> <li>16 Sectors (default if a drive is installed)</li> </ul>                                                                                                                                                                                                                                          |

|                        | <b>Note</b> : This field displays only when the Type field contains a value of [User] or [1–39]. Autotyping may change this value if the hard disk reports that it supports block accesses.                                                                                                               |

| LBA Mode Control       | Determines how the System BIOS references hard disk data. You can use this option only if both the hard disk being configured and the operating system support LBA (Logical Block Addressing). Autotyping may change this value if the hard disk reports that it supports LBA.                            |

|                        | You can select one of these:                                                                                                                                                                                                                                                                              |

|                        | • <b>Disabled (default if no drive is installed)</b> : Reference hard disk data using the CHS (Cylinders/Heads/Sectors) method.                                                                                                                                                                           |

|                        | • Enabled (default if a drive is installed): Reference hard disk data as logical blocks.                                                                                                                                                                                                                  |

|                        | <b>Note</b> : This field displays only when the Type field contains a value of [None].                                                                                                                                                                                                                    |

| Field          | Description                                                                                                                                                                                                                                                                             |                                          |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--|

| Transfer Mode  | Selects the mode that the System BIOS uses to access the hard disk.  You can select one of these:                                                                                                                                                                                       |                                          |  |

|                |                                                                                                                                                                                                                                                                                         |                                          |  |